Make 빌드 시스템 2

- 개발자라면?/Linux

- 2022. 9. 2.

5. Make 빌드 시스템 1

Build - 한번에 .c 로 빌드하지 말고 각각의 obejct 파일을 만들고 링킹해서 실행파일을 만드는 것이 효율적이다!! object 만들기 실행 파일 만들기 Make 자동 빌드 도구!!! Makefile 이 있어야 사용 가능 >>

kay-dev.tistory.com

Suffix Rules

Suffilc Rules (확장자 규칙)은 미리 정의해 놓은 일반화한 기술 파일 항목을 의미한다.

Suffix Rules 1

OBJS = test1.o test2.o test3.o

CC = gcc

#CC = arm-gcc

CFLAGS = -g -O0 -Wall # flag for compile

LDFLAGS = -static # flag for linker

test: ${OBJS}

echo "Linking..."

${CC} -o $@ $^ ${LDFLAGS}

.c.o: # 모든 .c 에 대해 알아서 찾게 됨

${CC} -c ${CFLAGS} $<

# pony(dummy) target

clean:

-rm test1.o

-rm test2.o test3.o

# dependency

dep:

gccmakedep ${OBJS}Suffic Rules 2

- Default Suffic Rule 이 있으면 대부분 생략해도 자동으로 필요한 부분을 찾고 진행한다

(CC, Compile, Linker 에 대한 부분만 정의해주면 대부분은 자동으로 가능!!) - SRCS

OBJS = test1.o test2.o test3.o

SRCS = ${OBJS:.o=.c}

CC = gcc

#CC = arm-gcc

CFLAGS = -g -O0 -Wall # flag for compile

LDFLAGS = -static # flag for linker

test: ${OBJS}

echo "Linking..."

${CC} -o $@ $^ ${LDFLAGS}

# pony(dummy) target

clean:

-rm test1.o

-rm test2.o test3.o

# dependency

dep:

gccmakedep ${SRCS}

- 다중 Target 생성

- make 한 번으로 모든 target 을 빌드하게 해보자

- all 이라는 변수에 빌드할 모든 target 을 prerequisites로 담아두면 된다

OBJS = test1.o test2.o test3.o

SRCS = ${OBJS:.o=.c}

SRCS2 = exam2.c test2.c

OBJS2 = ${SRCS2: .c=.o}

CC = gcc

#CC = arm-gcc

CFLAGS = -g -O0 -Wall # flag for compile

LDFLAGS = -static # flag for linker

all: test exam2

test: ${OBJS}

echo "Linking..."

${CC} -o $@ $^ ${LDFLAGS}

exam2: ${OBJS2}

${CC} -o $@ $^ ${LDFLAGS}

# pony(dummy) target

clean:

-rm ${OBJS}

-rm test

-rm ${OBJS2}

-rm exam2

# dependency

dep:

gccmakedep ${SRCS}

- make 의 중요 옵션들

| 옵션 | 의미 |

| -C <dir> | Makefile 을 계속 읽지 말고 우선은 dir로 이동 |

| -d | make 를 수행함녀서 각종 디버깅 정보를 모두 출력 |

| -h | make 옵션에 대한 도움말 출력 |

| -f <name> | name 에 해당하는 파일을 makefile 로 취급 |

| -r | 내장하고 있는 각종 규칙 (suffix rule 등) 을 없는 것으로 간주함 |

| -t | 파일의 생성 날짜를 현재 시간으로 갱신 |

| -v | make 유틸리티의 버전을 출력함 |

| -p | make 에서 내부적으로 설정되어 있는 값들을 출력함 |

| -s | make 가 실행하는 명령어를 출력하지 않고 실행함 |

| -n | 실행될 명령을 출력만 함 (실행은 하지 않음) |

| -l | make 는 에러가 발생하면 도중에 실행을 중단하는데, 에러가 나도 실행을 멈추지 않고 계속 진행함 (에러무시) |

Quiz

- 아래 .............. 을 채우면?? (답은 더보기 Click!)

##

## Makefile : for Static/Shared/Dynamic Library Programming

##

PLATFORM =

CC = $(PLATFORM)gcc

CFLAGS = -Wall -O2

ARFLAGS = -rcs

....................

clean :

-rm -f $(LIB_OBJS)

-rm -f libtest.aPLATFORM =

LIB_OBJS = min.o max.o

CC = $(PLATFORM)gcc

CFLAGS = -Wall -O2

ARFLAGS = -rcs

libtest.a: ${LIB_OBJS}

${AR} ${ARFLAGS} $@ $^

clean :

-rm -f $(LIB_OBJS)

-rm -f libtest.a

- 아래 ________ 를 채우면? (답은 더보기 Click!)

##

## Makefile : for Static/Shared/Dynamic Library Programming

##

PLATFORM =

INC_PATH = ________

CC = $(PLATFORM)gcc

CFLAGS = ________

LIB_PATH_STATIC = _______

app : app.o

@echo "app create using static library...."

___________

___________

clean :

___________

-rm -f app app.o##

## Makefile : for Static/Shared/Dynamic Library Programming

##

PLATFORM =

INC_PATH = ../include

CC = $(PLATFORM)gcc

CFLAGS = -g -O0 -Wall -I${INC_PATH}

LIB_PATH_STATIC = ../libStatic

LDFLASG= -static

app : app.o

@echo "app create using static library...."

${MAKE} -C ${LIB_PATH_STATIC} # 어플의 입장에서는 libStatic 으로 가서 make 를 돌려야함

${CC} ${LDFLAGS} $^ -ltest -L${LIB_PATH_STATIC}

clean :

${MAKE} -C ${LIB_PATH_STATIC} clean

-rm -f app app.o

- Target-specific

- target 에 따라 다른 variable 을 지정해주고 싶을 때!!

- 아래의 'task2 : LDFLAGS = -static '

CC = gcc

CFLAGS = -O2 -Wall -g

SRCS = test1.c test2.c test3.c

OBJS = $(SRCS:.c=.o)

LIB_OUT = libtest.so

APP_OBJ = task1.o task2.o

APP_OUT = $(APP_OBJ:.o=)

test: $(LIB_OUT) $(APP_OUT)

$(LIB_OUT) : LDFLAGS = -shared

$(LIB_OUT) : lib/min.o lib/max.o

$(CC) $(LDFLAGS) -o $@ $^

task1 : LDFLAGS =

task1 : task1.o

$(CC) $(LDFLAGS) -o $@ $<

task2 : LDFLAGS = -static

task2 : task2.o

$(CC) $(LDFLAGS) -o $@ $<

lib/%.o : CFLAGS = -fPIC -O2 -Wall -g

clean:

-rm -f lib/*.o

-rm $(APP_OUT) $(APP_OBJ) $(LIB_OUT)

- Macro Assignment Operator

| operator | 용도 | 예시 | |

| = (recursive) |

recursively expanded variable (뒤쪽의 실행까지 고려) |

foo = $(bar) bar = $(hug) ugh = Huh? all:;echo $(foo) |

CFLAGS = $(include_dirs) -O include_dirs = Ifoo -Ibar |

| := or ::= (simple) |

simply expanded variables | x := foo y := $(x) bar x := later |

|

| ?= (conditional) |

conditional variable (조건부 실행) |

FOO ?= bar | it only has an effect if the variable is not yet defined |

| += (appending) |

add to variable's value | variable := value variable += more |

variable := value variable := $(variable) more |

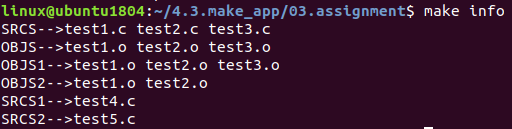

CC = gcc

CFLAGS = -O2 -Wall -g

SRCS = test1.c test2.c

OBJS1 = $(SRCS:.c=.o)

OBJS2 := $(SRCS:.c=.o)

SRCS += test3.c

OBJS = $(SRCS:.c=.o)

SRCS1 = test4.c

SRCS1 ?= test5.c

SRCS2 ?= test5.c

test: $(OBJS)

$(CC) -o $@ $^

info:

@echo -n "SRCS-->"

@echo $(SRCS)

@echo -n "OBJS-->"

@echo $(OBJS)

@echo -n "OBJS1-->"

@echo $(OBJS1)

@echo -n "OBJS2-->"

@echo $(OBJS2)

@echo -n "SRCS1-->"

@echo $(SRCS1)

@echo -n "SRCS2-->"

@echo $(SRCS2)

clean:

rm $(OBJS) test

dep:

gccmakedep $(SRCS)

- Directory 제어를 위한 Internal Macro

| Macro | 의미 |

| $(@D) | 목표 파일 이름의 directory 부분, 뒤에 슬래시가 제거됨 |

| $(@F) | 목표 파일 이름의 파일 부분, $(notdir $@) 과 동일함 |

| $(*D), $(*F) | The directory part and the file-within-directory part of the stem. |

| $(%D), $(%F) | The directory part and the file-within-directory part of the target archive member name. |

| $(<D), $(<F) | The directory part and the file-within-directory part of the first prerequisite. |

| $(^D), $(^F) | Lists of the directory parts and the file-within-directroy parts of all prerequisites |

| $(?D), $(?F) | Lists of the directory parts and the file-within-directory part of all prerequisites that are newer than the target. |

참고

GNU Make 강좌

doc.kldp.org

GNU Make 강좌: Makefile를 작성할 때 알면 좋은 것들

이전페이지 다음페이지 차례 Makefile을 작성할 때 기본적으로 알고 있으면 유익한 것들을 기술한다. 이전 강좌의 내용을 대체로 이해하고 있다면 좋은 팁이 될 것이다. 메뉴얼에 나오는 광범위한

doc.kldp.org

'개발자라면? > Linux' 카테고리의 다른 글

| iPerf3 설치 및 사용법 (0) | 2022.09.14 |

|---|---|

| IP 설정, 확인하기 (0) | 2022.09.14 |

| Make 빌드 시스템 1 (0) | 2022.09.02 |

| 라이브러리의 동작과 제작 (0) | 2022.09.02 |

| GNU (0) | 2022.09.02 |